PWM Step-Up DC-DC Converter

### Features

- Low Start-Up Voltage 0.9V

- Fixed 300kHz Operating Frequency

- Built-In Internal Soft-Start Circuit

- Low Operating Current

- 3.3V and 5V (±2.5%) Fixed (APW7077) or Adjustable Output Voltage (APW7077A)

- High Efficiency Up to 88% at 400mA

Output Current

- High Output Current Up to 1A

- Compact Package: SOT-23-5

- Lead Free and Green Devices Available

(RoHS Compliant)

## **Applications**

- Cellular and Portable Phones

- Portable Audio

- Camcorders and Digital Still Camera

- Hand-held Instrument

- PDAs

### **General Description**

The APW7077/A series are multi- function PWM step-up DC-DC converter with an adaptive voltage mode controller and higher efficiency application from one to four cells battery packs. The APW7077/A series are set PWM operating mode, voltage-mode to follow portable application. And built-in driver pin, EXT pin, for connecting to an external transistor or MOSFET during light load, the device will automatically skip switching cycles to maintain high efficiency. The APW7077/A series consist of PWM controller, reference voltage, phase compensation, oscillator, soft-start, driver block. It will be provided to operate suitable voltage without external compensation circuit. The APW7077/A series have fixed voltage and adjustable voltage version from a wide input voltage ranges 0.7V to 5.5V for step-up DC-DC converter. The start-up is guaranteed at 1V and the device is operating down to 0.7V, and providing up to 300mA loading current. Besides, low quiescent current (switch-off) is guaranteed.

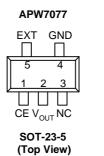

### **Pin Configuration**

EXT GND

APW7077A

FB V<sub>DD</sub> CE SOT-23-5 (Top View)

ANPEC reserves the right to make changes to improve reliability or manufacturability without notice, and advise customers to obtain the latest version of relevant information to verify before placing orders.

Copyright © ANPEC Electronics Corp. Rev. A.7 - Jun., 2009

## Ordering and Marking Information

| APW7077/A     |      | Assembly Material<br>Handling Code<br>Temperature Range<br>Package Code<br>Voltage Code | Package Code<br>B : SOT-23-5<br>Temperature Range<br>I : -40 to 85 °C<br>Handling Code<br>TR : Tape & Reel<br>Voltage Code<br>R : 3.3V Z : 5.0V<br>Assembly Material<br>G : Halogen and Lead Free Device |

|---------------|------|-----------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| APW7077A B:   | A77X |                                                                                         | X - Date Code                                                                                                                                                                                            |

| APW7077 33B:  | 77RX |                                                                                         | X - Date Code; R : 3.3V                                                                                                                                                                                  |

| APW7077 50B : | 77ZX |                                                                                         | X - Date Code; Z : 5.0V                                                                                                                                                                                  |

Note : ANPEC lead-free products contain molding compounds/die attach materials and 100% matte tin plate termination finish; which are fully compliant with RoHS. ANPEC lead-free products meet or exceed the lead-free requirements of IPC/JEDEC J-STD-020C for MSL classification at lead-free peak reflow temperature. ANPEC defines "Green" to mean lead-free (RoHS compliant) and halogen free (Br or CI does not exceed 900ppm by weight in homogeneous material and total of Br and CI does not exceed 1500ppm by weight).

### Absolute Maximum Ratings (Note 1)

| Symbol           | Parameter                                      | Rating      | Unit |

|------------------|------------------------------------------------|-------------|------|

| V <sub>DD</sub>  | Supply Voltage                                 | -0.3 to 7   | V    |

| V <sub>IO</sub>  | Input / Output Pins (CE, FB, EXT)              | -0.3 to 7   | V    |

| T <sub>A</sub>   | Operating Ambient Temperature Range            | -40 to 85   | °C   |

| TJ               | Junction Temperature Range                     | -40 to 150  | °C   |

| T <sub>STG</sub> | Storage Temperature Range                      | -65 to +150 | °C   |

| Ts               | Maximum Lead Soldering Temperature, 10 Seconds | 260         | °C   |

Note 1: Absolute Maximum Ratings are those values beyond which the life of a device may be impaired. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

### **Thermal Characteristics**

| Symbol              | Parameter                                                     | Typical Value | Unit |

|---------------------|---------------------------------------------------------------|---------------|------|

| $R_{	ext{	heta}JA}$ | Thermal Resistance – Junction to Ambient (Note 2)<br>SOT-23-5 | 200           | °C/W |

Note 2:  $\theta_{IA}$  is measured with the component mounted on a high effective thermal conductivity test board in free air.

## **Electrical Characteristics**

(For all values  $\rm T_{A}$  = 25°C,  $\rm V_{OUT}$  = 3.3V, unless otherwise noted)

| Symbol            | Parameter                            | Test Conditions                                         | 4    | APW7077A |      |      |

|-------------------|--------------------------------------|---------------------------------------------------------|------|----------|------|------|

| Symbol            | Parameter                            | Test Conditions                                         | Min. | Тур.     | Max. | Unit |

| STEP-UP           | SECTION                              |                                                         |      | •        |      |      |

| V <sub>IN</sub>   | Minimum Operating Input Voltage      | $V_{OUT} = V_{DD}$                                      | -    | 0.9      | -    | V    |

| V <sub>DD</sub>   | Operating Voltage                    | V <sub>IN</sub> = V <sub>DD</sub>                       | 1.9  | -        | 5.5  | V    |

|                   | Start-Up Voltage                     | $I_0 < 10 \text{mA}, V_{OUT} = V_{DD} (< 5.5 \text{V})$ | -    | 0.9      | 1    | V    |

|                   |                                      | $V_{OUT} = 12V$ , Io<10mA, $V_{DD} = V_{IN}$            | 1.9  | 2.0      | -    | V    |

| f <sub>SW</sub>   | Operating Frequency                  | $V_{DD} = 3.3 V, V_{FB} = 0.5 V$                        | 270  | 300      | 330  | kHz  |

|                   | Oscillator Frequency Line Regulation | 2.0V <v<sub>DD&lt;5.5V</v<sub>                          | -    | ±1.2     | -    | %    |

| D <sub>MAX</sub>  |                                      |                                                         | 81   | 88       | 95   | %    |

|                   | Maximum Duty Line Regulation         | 2.0V <v<sub>DD&lt;5.5V</v<sub>                          | -    | ±0.5     | -    | %    |

| POWER             | MOSFET                               | •                                                       | ·    | •        | •    |      |

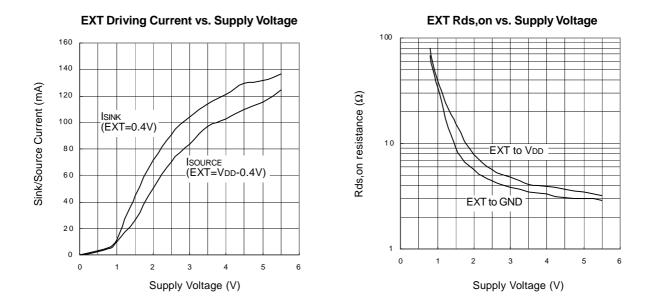

| ISOURCE           | EXT Output Source Current            | Duty≤5%, EXT = V <sub>DD</sub> -0.4V                    | -70  | -110     | -150 | mA   |

| I <sub>SINK</sub> | EXT Output Sink Current              | Duty≤5%, EXT = 0.4V                                     | 80   | 120      | 160  | mA   |

| CONTRO            | LSECTION                             |                                                         |      | •        |      |      |

|                   | Output Voltage Range                 | External Divider                                        | 2.0  | -        | -    | V    |

| $V_{FB}$          | Feedback Voltage                     | I <sub>LOAD</sub> = 0mA                                 | 0.98 | 1        | 1.02 | V    |

|                   | Feedback Voltage Line Regulation     | 2.0V <v<sub>DD&lt;5.5V</v<sub>                          | -    | ±0.1     | -    | %    |

| I <sub>FB</sub>   | Feedback Input Current               | V <sub>FB</sub> = 1.4V                                  | -    | 0.03     | 50   | nA   |

| T <sub>ss</sub>   | Soft-Start Time                      |                                                         | 10   | 25       | 40   | ms   |

|                   | Soft-Start Threshold Voltage         | Duty = 50%                                              | -    | 1.65     | -    | V    |

|                   | Soft-Start Hysteresis Voltage        |                                                         | -    | 150      | -    | mV   |

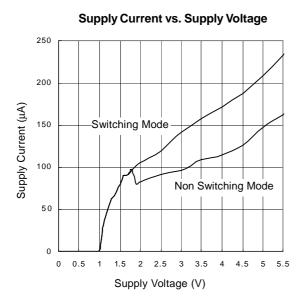

| 1.00              | On anothing Councert                 | $V_{DD} = V_{CE} = 3.3 V, V_{FB} = 0.5 V$               | -    | 150      | 230  | μA   |

| lq                | Operating Current                    | $V_{DD} = V_{CE} = 3.3V, V_{FB} = 1.1V$                 | -    | 100      | 150  | μA   |

| I <sub>OFF</sub>  | Stand-by Current                     | $V_{DD} = V_{CE} = 3.3V, V_{FB} = 1.3V$                 | -    | 17       | 25   | μA   |

|                   | Switch-Off Current                   | $V_{DD} = 3.3 V, V_{CE} = 0 V$                          | -    | 1        | 2    | μA   |

| $V_{CE}$          | Logic LOW (V <sub>IL</sub> )         |                                                         | -    | -        | 0.7  | V    |

|                   | Logic HIGH(V <sub>IH</sub> )         |                                                         | 1.2  | -        | -    | V    |

| $I_{CE}$          | CE Pin Input Current                 | $V_{CE} = 0V$                                           | -    | 1        | 2    | μA   |

|                   |                                      | V <sub>CE</sub> = 3.3V                                  | -    | 0.07     | 50   | nA   |

# **Electrical Characteristics (Cont.)**

(For all values  $\rm T_{_A}$  = 25°C,  $\rm V_{_{OUT}}$  = 3.3V, unless otherwise noted)

| Symbol            | Baramatar                       | Test Conditions                                                                          |       | APW7077 |       |      |  |

|-------------------|---------------------------------|------------------------------------------------------------------------------------------|-------|---------|-------|------|--|

| Symbol            | Parameter                       | Test Conditions                                                                          | Min.  | Тур.    | Max.  | Unit |  |

| STEP-UP           | SECTION                         |                                                                                          |       |         |       |      |  |

| V <sub>IN</sub>   | Minimum Operating Input Voltage |                                                                                          | 0.7   | -       | -     | V    |  |

|                   | Operating Voltage               |                                                                                          | 1     | -       | 5.5   | V    |  |

|                   |                                 | APW7077_33, lo<10mA                                                                      | -     | 0.9     | -     | V    |  |

|                   |                                 | APW7077_33, 10mA <lo<100ma< td=""><td>-</td><td>1.1</td><td>-</td><td>V</td></lo<100ma<> | -     | 1.1     | -     | V    |  |

|                   | Start-Up Voltage                | APW7077_50, lo<10mA                                                                      | -     | 0.9     | -     | V    |  |

|                   | ]                               | APW7077_50, 10mA <lo<100ma< td=""><td>-</td><td>1.1</td><td>-</td><td>V</td></lo<100ma<> | -     | 1.1     | -     | V    |  |

| $V_{\text{HOLD}}$ | Hold Voltage                    | I <sub>LOAD</sub> = 10mA                                                                 | -     | 0.7     | 0.8   | V    |  |

| f <sub>sw</sub>   | Operating Frequency             | V <sub>OUT</sub> = 3.3VX96%                                                              | 270   | 300     | 330   | kHz  |  |

| D <sub>MAX</sub>  | Maximum Duty Cycle              | ximum Duty Cycle V <sub>OUT</sub> = 3.3VX96%                                             |       | 88      | 95    | %    |  |

| POWER M           | IOSFET                          |                                                                                          |       |         | ,     |      |  |

| ISOURCE           | EXT Output Source Current       | Duty≤5%, EXT = 2.9V                                                                      | -70   | -110    | -150  | mA   |  |

| I <sub>SINK</sub> | EXT Output Sink Current         | Duty≤5%, EXT = 0.4V                                                                      | 80    | 120     | 160   | mA   |  |

| CONTROL           | SECTION                         |                                                                                          | •     |         |       |      |  |

| N/                | APW7077-33                      | I <sub>IN</sub> = 0mA                                                                    | 3.218 | 3.3     | 3.383 | V    |  |

| V <sub>OUT</sub>  | APW7077-50                      | I <sub>IN</sub> = 0mA                                                                    | 4.875 | 5       | 5.125 | V    |  |

| T <sub>SS</sub>   | Soft-Start Time                 |                                                                                          | 10    | 25      | 40    | ms   |  |

|                   | Soft-Start Threshold Voltage    | Duty = 50%                                                                               | -     | 1.65    | -     | V    |  |

|                   | Soft-Start Hysteresis Voltage   |                                                                                          | -     | 150     | -     | mV   |  |

| lq                | Operating Current               | $V_{CE} = V_{OUT}, \ V_{OUT} = 0.96 V_{OUT}$                                             | -     | 200     | 300   | μA   |  |

| Ч                 |                                 | $V_{CE} = V_{OUT}, V_{OUT} = 1.04 V_{OUT}$                                               | -     | 160     | 240   | μA   |  |

| I <sub>OFF</sub>  | Stand-by Current                | $V_{CE} = V_{OUT}, V_{OUT} = 1.3 V_{OUT}$                                                | -     | 35      | 55    | μA   |  |

|                   | Switch-Off Current              | V <sub>CE</sub> = 0V                                                                     | -     | 1       | 2     | μA   |  |

| V <sub>CE</sub>   | Logic LOW (VIL)                 |                                                                                          | -     | -       | 0.7   | V    |  |

|                   | Logic HIGH (V <sub>IH</sub> )   |                                                                                          | 1.2   | -       | -     | V    |  |

| I <sub>CE</sub>   | CE Pin Input Current            | V <sub>CE</sub> = 0V                                                                     | -     | 1       | 2     | μA   |  |

|                   |                                 | V <sub>CE</sub> = 2.0V                                                                   | -     | 0.07    | 50    | nA   |  |

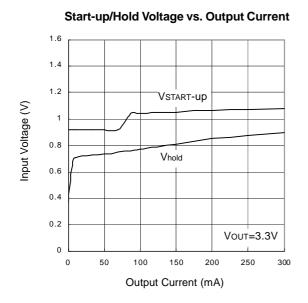

# **Typical Operating Characteristics**

1.6 1.4 1.2 VSTART-up Input Voltage (V) 1 0.8 Vhold 0.6 0.4 0.2 VOUT=5.0V 0 0 50 100 150 200 250 300 Output Current (mA)

#### Start-up/Hold Voltage vs. Output Current

Efficiency vs. Output Current Efficiency vs. Output Current 100 100 90 90 VDD=3V 80 80 VDD=5V \_VDD=2V 70 Efficiency(%) 70 Efficiency(%) VDD=3.3V 60 60 50 50 40 40 30 30 Vout=12V ⁻Voυτ=5V L=10μΗ L=10µF 20 20 10 100 1 1 10 100 1000 Output Current (mA) Output Current (mA)

#### Copyright © ANPEC Electronics Corp. Rev. A.7 - Jun., 2009

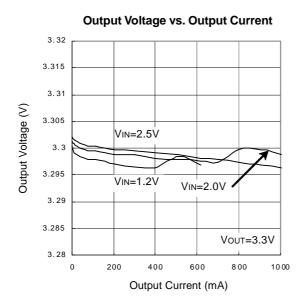

# **Typical Operating Characteristics (Cont.)**

#### **Output Voltage vs. Temperature Oscillation Frequency vs. Temperature** 3.40 3 30 3.38 3 20 3.36 Oscillation Frequency (kHz) 3.34 Output Voltage (V) 3 10 3.32 3.30 3 00 3.28 2 90 3.26 3.24 280 3.22 3.20 270 -40 -20 0 20 40 60 80 -20 0 20 40 80 -40 60 Temperature (°C) Temperature (°C)

Copyright © ANPEC Electronics Corp. Rev. A.7 - Jun., 2009

# **Typical Operating Characteristics (Cont.)**

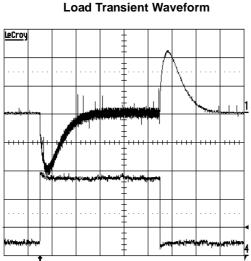

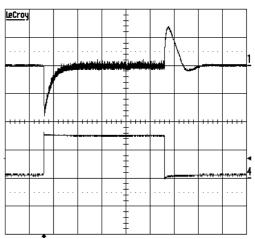

VIN=3.3<sup>1</sup>V, Vout=12V, Iout=5mA->50mA->5mA L=10μH, Cout=4.7μF+0.1μF, Cff=560pF CH1:Vout, 100mV/DIV, Time=1ms/DIV CH4:Iout, 20mA/DIV

Load Transient Waveform

#### Copyright © ANPEC Electronics Corp. Rev. A.7 - Jun., 2009

VIN=3.3V, VOUT=5V, IOUT=10mA->300mA->10mA L=10µH, COUT=22µF+22µF+0.1µF, Cff=33pF CH1:VOUT, 100mV/DIV, Time=1ms/DIV CH4:IOUT, 200mA/DIV

# **Typical Operating Characteristics (Cont.)**

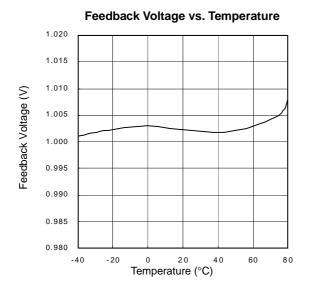

Feedback Voltage vs. Supply Voltage

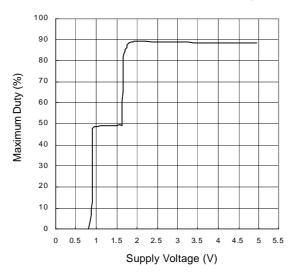

Maximum Duty vs. Supply Voltage

Copyright © ANPEC Electronics Corp. Rev. A.7 - Jun., 2009

# **Typical Operating Characteristics (Cont.)**

# **Pin Descripition**

|         | PIN      |                  |                                                                                                                                                   |  |

|---------|----------|------------------|---------------------------------------------------------------------------------------------------------------------------------------------------|--|

| N       | 0.       | NAME             | FUNCTION                                                                                                                                          |  |

| APW7077 | APW7077A |                  |                                                                                                                                                   |  |

| 1       | 3        | CE               | Chip enable input. High = operating mode; Low = shutdown mode                                                                                     |  |

| 5       | 5        | EXT              | External MOSFET or transistor drive pin.                                                                                                          |  |

| 4       | 4        | GND              | Ground pins of the circuit.                                                                                                                       |  |

| -       | 2        | V <sub>DD</sub>  | Supply voltage.                                                                                                                                   |  |

| -       | 1        | FB               | FB: Internal 1.0V reference voltage. Use a resistor divider to set the output voltage from and $V_{OUT} = \left(1 + \frac{R2}{R1}\right)V_{FB}$ . |  |

| 3       | -        | NC               | No internal connection to the pin.                                                                                                                |  |

| 2       | -        | V <sub>OUT</sub> | V <sub>OUT</sub> Provides bootstrap power to the IC.                                                                                              |  |

Copyright  $\circledcirc$  ANPEC Electronics Corp. Rev. A.7 - Jun., 2009

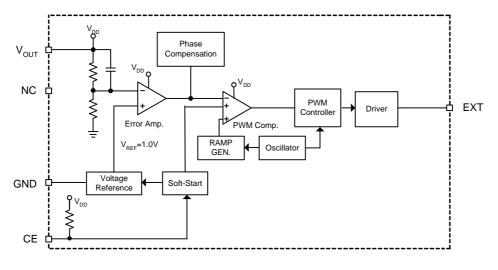

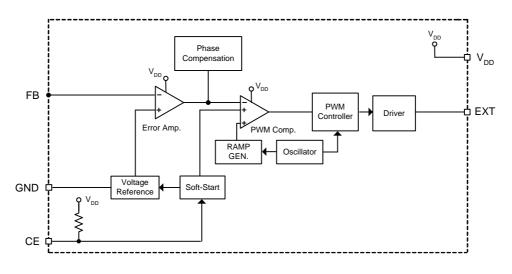

# **Block Diagram**

APW7077A

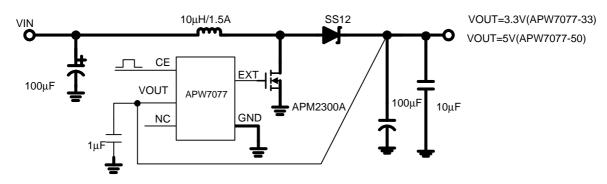

# **Typical Application Circuit**

Application Circuit for APW7077

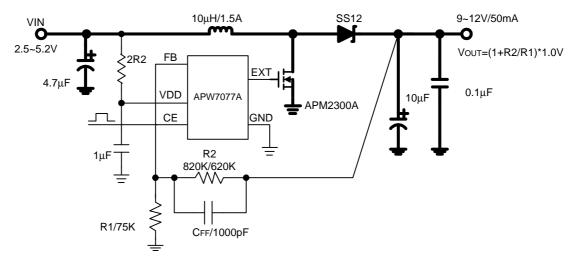

Application Circuit for APW7077A

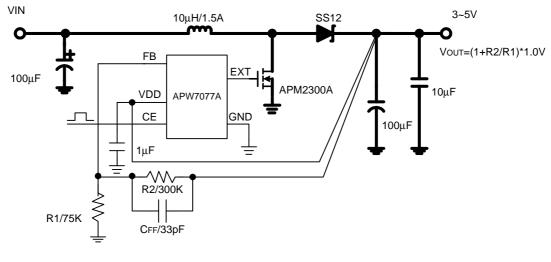

Application Circuit for APW7077A

\*R1 100K $\Omega$  is recommended

Copyright © ANPEC Electronics Corp. Rev. A.7 - Jun., 2009

### **Function Description**

#### Operation

The APW7077/A series are low noise fixed frequency voltage-mode PWM DC-DC controllers, and consist of startup circuit, reference voltage, oscillator, loop compensation network, PWM control circuit, and low ON resistance driver.

APW7077 provides on-chip feedback resistor and loop compensation network, the system designer can get the regulated fixed output voltage 3.3V and 5.0V with a small number of external components, it is optimized for battery powered portable products where large output current is required. APW7077A provides internal reference voltage 1.0V and output voltage setting by external resistance for higher voltage requirement. The quiescent current is typically 120 $\mu$ A (V<sub>OUT</sub> = 3.3V, fsw = 300kHz), and can be further reduced to about 1.0 $\mu$ A when the chip is disabled (V<sub>OEF</sub> < 0.7V).

The APW7077/A operation can be best understood by referring to the block diagram. The error amplifier monitors the output voltage via the feedback resistor divider by comparing the feedback voltage with the reference voltage. When the feedback voltage is lower than the reference voltage, the error amplifier output will decrease. The error amplifier output is then compared with the oscillator ramp voltage at the PWM controller.

When the feedback voltage is higher than the reference voltage, the error amplifier output increases and the duty cycle decreases. When the external power switch is on, the current ramps up in the inductor, storing energy in the magnetic field. When the external power switch is off, the energy stored in the magnetic field is transferred to the output filter capacitor and the load. The output filter capacitor stores the charge while the inductor current is higher than the output current, and then sustains the output voltage until the next switching cycle.

As the load current decreases, the switch transistor turns on for a shorter duty cycle. Under the light load condition, the controller will skip switching cycles to reduce power consumption, therefore, high efficiency is maintained at light loads.

#### Fixed Output Voltage (for APW7077 Only)

The APW7077  $V_{OUT}$  is set by an integrate feedback resistor network. This is trimmed to a selected voltage 3.3V or 5.0V with an accuracy of +/-2.5%.

#### Setting Output Voltage (for APW7077A only)

For APW7077A, the output voltage is adjustable. The output voltage is set using the FB pin and a resistor divider connected to the output as shown in the typical operating circuit. The internal reference voltage is 1.0V with 2% variation, so the ratio of the feedback resistors sets the output voltage according to the following equation:

$$V_{OUT} = (1 + \frac{R2}{R1}) \times 1.0V$$

To avoid the thermal noise from feedback resistor,  $(R_1+R_2)$  resistance smaller than  $1m\Omega$  and 1% variation is recommended.

#### Soft-Start

There is a soft-start function integrated in APW7077/A series to avoid the over shooting when power on. When power is applied to the device, the soft-start circuit first pumps up the output voltage to let  $V_{DD}$  (or  $V_{OUT}$ ) approximately 1.65V at a fixed duty cycle 50%. This is the voltage level at which the controller can operate normally. When supply voltage more than 1.65V, the internal reference voltage will be ramp up to let output voltage reach to setting voltage without over shooting issue whenever heavy load or light load condition. The soft-start time 25ms is setting by internal circuit.

#### Oscillator

The oscillator frequency is internally set to 300kHz at an accuracy of +/-10% and with low temperature coefficient of 3.3%/°C.

#### **Enable/Disable Operation**

The APW7077/A series offer IC shutdown mode by chip enable pin (CE pin) to reduce current consumption. When voltage at pin CE is greater than 1.2V, the chip will be enabled, which means the controller is in normal operation. When voltage at pin CE is less than 0.7V, the chip is disabled, which means IC is shutdown and quiescent current becomes  $1\mu$ A.

# Function Description (Cont.)

#### Enable/Disable Operation (Cont.)

The CE pin is pulled high to  $V_{DD}$  (or  $V_{OUT}$ ) by internal resistor, and this resistance is greater than  $1m\Omega$ . Therefore, this chip will enable normally when CE pin is floating. Important: DO NOT apply a voltage between 0.7V and 1.2V

to pin CE as this is the CE pin's hysteresis voltage range. Clearly defined output states can only be obtained by applying voltage out of this range.

#### Compensation

The device is designed to operate in continuous conduction mode. An internal compensation circuit was designed to guarantee stability over the full input/output voltage and full output load range.

#### Step-Up Converter Operating Mode

The step-up DC-DC controller is designed to operate in continuous conduction mode (CCM) or discontinuous conduction mode (DCM).

For a step up converter in a CCM, the duty cycle D is given by:

$$\mathsf{D} = \frac{\mathsf{V}_{\mathsf{OUT}} - \mathsf{V}_{\mathsf{IN}}}{\mathsf{V}_{\mathsf{OUT}}}$$

In higher output voltage or small output current application, the step-up DC-DC controller operated in discontinuous conduction mode almost. For a step-up converter in a DCM, the duty cycle D is given by:

$$D = \sqrt{\frac{2 \cdot L}{T_{S} \cdot R_{LOAD}} \cdot \frac{V_{OUT}}{V_{IN}} \left(\frac{V_{OUT}}{V_{IN}} - 1\right)}$$

External components values can be calculated from these equations, however, the optimized value should obtained through experimental results.

#### **Critical Inductance Value**

The minimum value of inductor to maintain continuous conduction mode can be determined by the following equation.

$$L \geq \frac{V_{OUT} \times D(1 - D)^2}{f_{SW} \times I_O \times Ratio}$$

Copyright © ANPEC Electronics Corp. Rev. A.7 - Jun., 2009 A system can be designed to operate in continuous mode for load currents above a certain level usually 20 to 50% (Ratio define as 0.2~0.5) of full load at minimum input voltage. When  $I_o$  smaller than ( $I_o$ \*Ratio), the controller system will into DCM.

$\Delta I_{L}$  is the ripple current flowing through the inductor, which affects the output voltage ripple and core losses. Based on 20%(Ratio=0.2) current ripple, V<sub>OUT</sub>=5V, I<sub>o</sub>=1A and V<sub>IN</sub> =1.8V system, the inductance value is calculated as 6.9µH and a 6.8µH inductor is used.

The inductor current ripple has an expression :

$$\Delta I_{L} = \frac{V_{IN} \times D}{f_{SW} \times L}$$

The maximum DC input current can be calculated as :

$$I_{L}(max) = \frac{V_{OUT} \times I_{O}(max)}{V_{IN}(min)}$$

The inductor peak current can be calculated as :

$$I_{PK} = \frac{V_{OUT} \times I_{O}}{V_{IN}} + \frac{\Delta I_{L}}{2}$$

Notes:

D - On-time duty cycle

I<sub>1</sub> - Average inductor current

I<sub>PK</sub> - Peak inductor current

I<sub>o</sub> - Desired dc output current

$V_{\mbox{\tiny IN}}$  - Nominal operating dc input voltage

V<sub>OUT</sub> - Desired dc output voltage

ESR - Equivalent series resistance of the output capacitor

#### **Inductor Selection**

APW7077/A series are designed to work well with a 6.8 to  $12\mu$ H inductors. In most applications,  $10\mu$ H is a sufficiently low value to allow the use of a small surface mount coil but large enough to maintain low ripple. Lower inductance values not only supply higher output current but also increase the ripple and reduce efficiency. Higher inductor values not only reduce ripple and improve efficiency but also limit output current. The inductor should have small DCR, usually less than  $0.2\Omega$ , to minimize loss. It is necessary to choose an inductor with a saturation current greater than the peak current which the inductor will encounter in the application.

# Function Description (Cont.)

#### Inductor Selection

The inductor ripple current is important for a few reasons. One reason is the peak switch current will be the average inductor current (I,) plus  $\Delta I_i$ .

As a side note, discontinuous operation occurs when the inductor current falls to zero during a switching cycle, or  $\Delta I_{L}$  is greater than the average inductor current. Therefore, continuous conduction mode occurs when  $\Delta I_{L}$  is less than the average inductor current. Care must be taken to make sure that the switch will not reach its current limit during normal operation.

The inductor must also be sized accordingly. It should have a saturation current rating higher than the peak inductor current expected. The output voltage ripple is also affected by the total ripple current.

#### **Output Capacitor**

The output capacitor is used for sustaining the output voltage when the external MOSFET or bipolar transistor is switched on and smoothing the ripple voltage.

The output capacitance needed is calculated in equation.

$$C_{OUT(min)} = \frac{I_{O(max)} \times D}{f_{SW} \times \Delta V_{OUT}}$$

The ESR is also important because it determines the peak to peak output voltage ripple according to the approximated equation:

$$\mathsf{ESR} = \frac{\Delta \mathsf{V}_{\mathsf{OUT}}}{\Delta \mathsf{I}_{\mathsf{O}}}$$

With 1% output voltage ripple, low ESR capacitor should be used to reduce output ripple voltage. In general, a 100 $\mu$ F to 220 $\mu$ F low ESR (0.10 $\Omega$  to 0.30 $\Omega$ ) Tantalum capacitor should be appropriate. The choice of output capacitors is also somewhat arbitrary and depends on the design requirements for output voltage ripple. A minimum value of 10 $\mu$ F is recommended and may be increased to a larger value.

#### **Input Capacitor**

The input capacitor can stabilize the input voltage and minimize peak current ripple from the source. The size used is dependant on the application and board layout. If the regulator will be loaded uniformly, with very little load

Copyright © ANPEC Electronics Corp. Rev. A.7 - Jun., 2009 changes, and at lower current outputs, the input capacitor size can often be reduced. The size can also be reduced if the input of the regulator is very close to the source output. The size will generally need to be larger for applications where the regulator is supplying nearly the maximum rated output or if large load steps are expected. A minimum value of  $10\mu$ F should be used for the less stressful conditions while a  $22\mu$ F to  $47\mu$ F capacitor may be required for higher power and dynamic loads. Small ESR Tantalum or ceramic capacitor should be suitable and the total input ripple voltage can be calculated:

$$\Delta V_{\text{IN}} = \Delta I_{\text{L}} \times \text{ESR}$$

#### **Design Example**

It is supposed that a step-up DC-DC controller with 3.3V output delivering a maximum 1000mA output current with 100 mV output ripple voltage powering from a 2.4V input is to be designed.

Design parameters:

$$V_{IN} = 2.4V$$

$$V_{OUT} = 3.3V$$

$$I_{o} = 1.0A$$

$$DV_{OUT} = 100mV$$

$$f_{SW} = 300kHz$$

Ratio = 0.2 (typical for small output ripple voltage) Assume the diode forward voltage and the transistor saturation voltage are both 0.3V. Determine the maximum steady state duty cycle at  $V_{IN} = 2.4V$ :

D=0.273

Calculate the maximum inductance value which can generate the desired current output and the preferred delta inductor current to average inductor current ratio:

L=10µH

Determine the average inductor current and peak inductor current:

```

I<sub>L</sub>=1.38A

∆I<sub>L</sub>=0.218A

Ipk=1.45A

```

Therefore, a  $10\mu H$  inductor with saturation current larger than 1.73A can be selected as the initial trial.

Determine the output capacitance value for the desired output ripple voltage:

C<sub>ουτ</sub>=33μF

# Function Description (Cont.)

#### Design Example (Cont.)

The ESR of the output capacitor is  $0.05\Omega$ . Therefore, a Tantalum capacitor with value of  $33\mu$ F to  $47\mu$ F and ESR of  $0.05\Omega$  can be used as the output capacitor. However, according to experimental result,  $220\mu$ F output capacitor gives better overall operational stability and smaller ripple voltage.

## **Component Selection**

#### **Diode Selection**

The output diode for a boost regulator must be chosen correctly depending on the output voltage and the output current. The diode must be rated for a reverse voltage equal to or greater than the output voltage used. The average current rating must be greater than the maximum load current expected, and the peak current rating must be greater than the peak inductor current. During short circuit testing, or if short circuit conditions are possible in the application, the diode current rating must exceed the switch current limit. The diode is the largest source of loss in DC-DC converters. The most importance parameters which affect their efficiency are the forward voltage drop, VF, and the reverse recovery time, tr. The forward voltage drop creates a loss just by having a voltage across the device while a current flowing through it. The reverse recovery time generates a loss when the diode is reverse biased, and the current appears to actually flow backwards through the diode due to the minority carriers being swept from the P-N junction. Using Schottky diodes with lower forward voltage drop will decrease power dissipation and increase efficiency.

#### **External Switch Transistor**

The APW7077/A can drive up to 110mA of gate drive current. An N-channel MOSFET with a relatively low threshold voltage, low gate charge and low RDS(ON) is required to optimize overall circuit performance. The APW7077/A Evaluation Board uses a APM2300A. This NMOS device was chosen because it demonstrates an RDS\_ON of  $45m\Omega$  and a total gate charge Qg of 12nC (typ.).

### Layout Consideration

#### **Ground Plane**

One point grounding should be used for the output power return ground, the input power return ground, and the device switch ground to reduce noise. The input ground and output ground traces must be thick enough for current to flow through and for reducing ground bounce.

#### **Power Signal Traces**

Low resistance conducting paths should be used for the power carrying traces to reduce power loss so as to improve efficiency (short and thick traces for connecting the inductor L can also reduce stray inductance). Trace connections made to the inductor and schottky diode should be minimized to reduce power dissipation and increase overall efficiency.

#### **Output Capacitor**

The output capacitor should be placed close to the output terminals to obtain better smoothing effect on the output ripple.

The output capacitor,  $C_{OUT}$ , should also be placed close to the diode. Any copper trace connections for the  $C_{OUT}$  capacitor can increase the series resistance, which directly effects output voltage ripple and efficiency.

#### Switching Noise Decoupling Capacitor

On APW7077 fixed voltage application, a 0.1 $\mu$ F ceramic capacitor should be placed close to the V<sub>out</sub> pin and GND pin of the chip to filter the switching spikes in the output voltage monitored by the V<sub>out</sub> pin.

#### Feedback Network

On APW7077A application, the feedback networks should be connected directly to a dedicated analog ground plane and this ground plane must connect to the GND pin. If no analog ground plane is available, this ground must tie directly to the GND pin. The feedback network, resis-

tors R1 and R2, should be kept close to the FB pin and away from the inductor, to minimize copper trace connections that can inject noise into the system. Prevent connect feedback network on output decoupling MLCC.

#### Input Capacitor

In APW7077A high output voltage application circuit, the input voltage ( $V_{IN}$ ) is tied to chip supply pin ( $V_{DD}$ ). The input capacitor  $C_{IN}$  in  $V_{IN}$  must be placed close to the IC. This will reduce copper trace resistance which effects input voltage ripple of the IC. For additional input voltage filtering, a 1µF capacitor can be placed in parallel with  $C_{IN}$ , close to the  $V_{DD}$  pin, to shunt any high frequency noise to the ground.

#### Inductor

To minimize copper trace connections that can inject noise into the system, the inductor, switch, and Schottky diode should be placed as close as possible to minimize the noise coupling into other circuits.

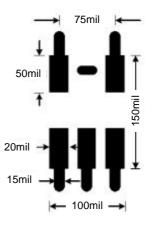

# Minimum Recommended Footprint for Surface Mounted Applications

Surface mount board layout is a critical portion of the total design. The footprint for the semiconductor packages must be the correct size to insure proper solder connection interface between the board and the package. With the correct pad geometry, the packages will self align when subjected to a solder reflow process.

Copyright © ANPEC Electronics Corp. Rev. A.7 - Jun., 2009

# Layout Consideration (Cont.)

Minimum Recommended Footprint for Surface Mounted Applications

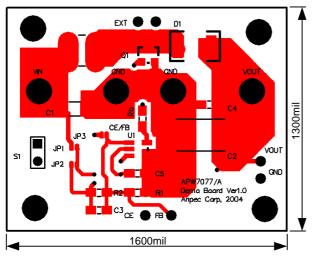

Demo Board Circuit Layout

**Top Layout**

**Bottom Layer**

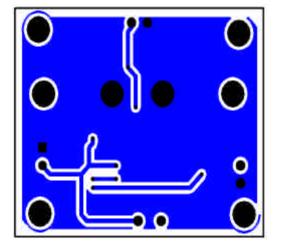

# Package Information

SOT-23-5

| Ş      |        | )T-23-5  |        |       |  |

|--------|--------|----------|--------|-------|--|

| SY MBO | MILLIM | ETERS    | INCHES |       |  |

| 2      | MIN.   | MAX.     | MIN.   | MAX.  |  |

| Α      |        | 1.45     |        | 0.057 |  |

| A1     | 0.00   | 0.15     | 0.000  | 0.006 |  |

| A2     | 0.90   | 1.30     | 0.035  | 0.051 |  |

| b      | 0.30   | 0.50     | 0.012  | 0.020 |  |

| с      | 0.08   | 0.22     | 0.003  | 0.009 |  |

| D      | 2.70   | 3.10     | 0.106  | 0.122 |  |

| E      | 2.60   | 3.00     | 0.102  | 0.118 |  |

| E1     | 1.40   | 1.80     | 0.055  | 0.071 |  |

| е      | 0.95   | BSC      | 0.03   | 7 BSC |  |

| e1     | 1.90   | 1.90 BSC |        | 5 BSC |  |

| L      | 0.30   | 0.60     | 0.012  | 0.024 |  |

| θ      | 0°     | 8°       | 0°     | 8°    |  |

Note : 1. Follow JEDEC TO-178 AA.

Dimension D and E1 do not include mold flash, protrusions or gate burrs. Mold flash, protrusion or gate burrs shall not exceed 10 mil per side.

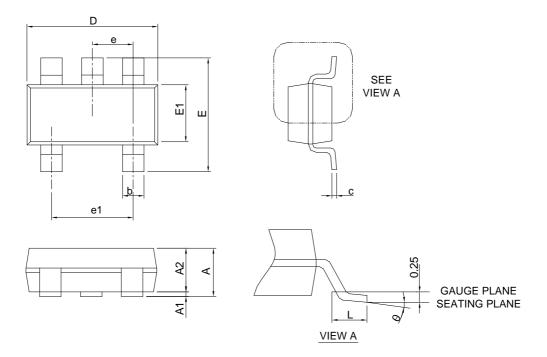

# **Carrier Tape & Reel Dimensions**

| Application | Α           | Н                 | T1                | С                  | d        | D                 | W                 | E1                 | F                  |

|-------------|-------------|-------------------|-------------------|--------------------|----------|-------------------|-------------------|--------------------|--------------------|

|             | 178.0 £2.00 | 50 MIN.           | 8.4+2.00<br>-0.00 | 13.0+0.50<br>-0.20 | 1.5 MIN. | 20.2 MIN.         | 8.0 <b>±</b> 0.30 | 1.75 <b>±</b> 0.10 | 3.5 <b>±</b> 0.05  |

| SOT-23-5    | P0          | P1                | P2                | D0                 | D1       | Т                 | A0                | B0                 | K0                 |

|             | 4.0 ±0.10   | 4.0 <b>±</b> 0.10 | 2.0 <b>±</b> 0.05 | 1.5+0.10<br>-0.00  | 1.0 MIN. | 0.6+0.00<br>-0.40 | 3.20 ±0.20        | 3.10 <b>±</b> 0.20 | 1.50 <b>±</b> 0.20 |

(mm)

### **Devices Per Unit**

| Package Type | Unit        | Quantity |

|--------------|-------------|----------|

| SOT-23-5     | Tape & Reel | 3000     |

Copyright © ANPEC Electronics Corp. Rev. A.7 - Jun., 2009

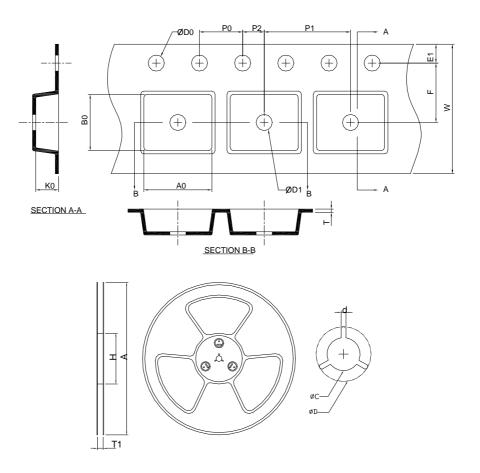

# **Taping Direction Information**

SOT-23-5

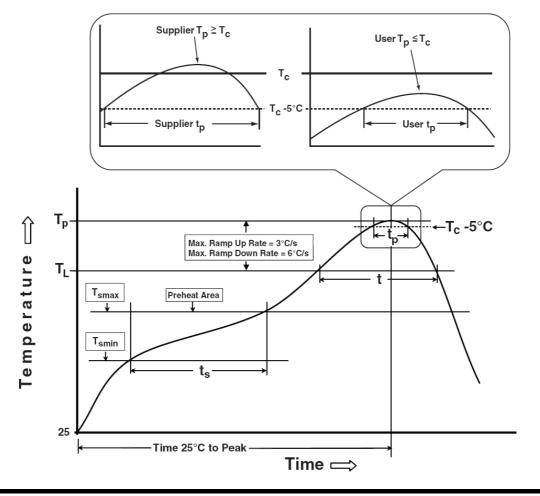

## **Classification Profile**

Copyright © ANPEC Electronics Corp. Rev. A.7 - Jun., 2009

## **Classification Reflow Profiles**

| Profile Feature                                                                                                                                                                                                         | Sn-Pb Eutectic Assembly            | Pb-Free Assembly                   |  |  |  |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------|------------------------------------|--|--|--|

| $\begin{array}{c} \textbf{Preheat \& Soak} \\ \textbf{Temperature min (T_{smin})} \\ \textbf{Temperature max (T_{smax})} \\ \textbf{Time (T_{smin} to T_{smax}) (t_s)} \end{array}$                                     | 100 °C<br>150 °C<br>60-120 seconds | 150 °C<br>200 °C<br>60-120 seconds |  |  |  |

| Average ramp-up rate<br>(T <sub>smax</sub> to T <sub>P</sub> )                                                                                                                                                          | 3 °C/second max.                   | 3°C/second max.                    |  |  |  |

| Liquidous temperature $(T_L)$<br>Time at liquidous $(t_L)$                                                                                                                                                              | 183 °C<br>60-150 seconds           | 217 °C<br>60-150 seconds           |  |  |  |

| Peak package body Temperature (T <sub>p</sub> )*                                                                                                                                                                        | See Classification Temp in table 1 | See Classification Temp in table 2 |  |  |  |

| Time $(t_P)^{**}$ within 5°C of the specified classification temperature $(T_c)$                                                                                                                                        | 20** seconds                       | 30** seconds                       |  |  |  |

| Average ramp-down rate ( $T_p$ to $T_{smax}$ )                                                                                                                                                                          | 6 °C/second max.                   | 6 °C/second max.                   |  |  |  |

| Time 25°C to peak temperature                                                                                                                                                                                           | 6 minutes max.                     | 8 minutes max.                     |  |  |  |

| * Tolerance for peak profile Temperature $(T_p)$ is defined as a supplier minimum and a user maximum.<br>** Tolerance for time at peak profile temperature $(t_p)$ is defined as a supplier minimum and a user maximum. |                                    |                                    |  |  |  |

#### Table 1. SnPb Eutectic Process – Classification Temperatures (Tc)

| Package<br>Thickness | Volume mm <sup>3</sup><br><350 | Volume mm <sup>3</sup><br>³350 |

|----------------------|--------------------------------|--------------------------------|

| <2.5 mm              | 235 °C                         | 220 °C                         |

| ≥2.5 mm              | 220 °C                         | 220 °C                         |

Table 2. Pb-free Process - Classification Temperatures (Tc)

| Package<br>Thickness | Volume mm <sup>3</sup><br><350 | Volume mm <sup>3</sup><br>350-2000 | Volume mm <sup>3</sup><br>>2000 |

|----------------------|--------------------------------|------------------------------------|---------------------------------|

| <1.6 mm              | 260 °C                         | 260 °C                             | 260 °C                          |

| 1.6 mm – 2.5 mm      | 260 °C                         | 250 °C                             | 245 °C                          |

| ≥2.5 mm              | 250 °C                         | 245 °C                             | 245 °C                          |

# **Reliability Test Program**

| Test item     | Method             | Description                  |

|---------------|--------------------|------------------------------|

| SOLDERABILITY | JESD-22, B102      | 5 Sec, 245°C                 |

| HOLT          | JESD-22, A108      | 1000 Hrs, Bias @ 125°C       |

| PCT           | JESD-22, A102      | 168 Hrs, 100%RH, 2atm, 121°C |

| тст           | JESD-22, A104      | 500 Cycles, -65°C~150°C      |

| НВМ           | MIL-STD-883-3015.7 | VHBM 2KV                     |

| MM            | JESD-22, A115      | VMM 200V                     |

| Latch-Up      | JESD 78            | 10ms, 1 <sub>tr</sub> 100mA  |